Obsah

Integrované systémy na čipu - vypracované otázky

1. Kdy a kým byl vynalezen integrovaný obvod?

1958 - Jack Kilby, Texas Instruments 1 Tranzistor a 4 Odpory na 1 čipu V roce 2000 udělena Nobelova cena

2. Jaké jsou dnešní nejmodernější technologie integrovaných obvodů? Napište hlavní vlastnosti a charakteristiky.

Vysoká integrace, šířka hradla 45nm - 410 milionů tranzistorů na ploše 107 mm2 (brzy 32nm), technologie MOSFET –> Dnes již 16nm. Např Sandy bridge 32nm nebo Ivy Bridge 22nm.

- CMOS (Complementary Metal Oxide Semiconductor) - dnes tradiční a nejběžnější technologie nějak uplatněná ve většině integrovaných součástek.

- SiGe (Silicon Germanium) - polovodičová technologie využívaná hlavně jako součást technologie BiCMOS pro velmi rychlé vysokofrekvenční součásky pro drátovou i bezdrátovou komunikaci a analogově-digitální zpracování velmi rychlých signálů.

- SOI (Silicon On Insulator) - polovodičová technologie určená a využívaná pro výrobu rychlých digitálních obvodů s velmi nízkou spotřebou a napájecím napětím

- ITFET (Inverted-T Field Effect Transistor) - technologie vytvářející prostorové (3D) provedení FET tranzistoru pro zmenšení velikosti čipu a snížení potřebného napájecího napětí.

3. Co jsou Moorovy zákony. Co popisují?

Zhruba 18 měsíců se zdvojnásobí počet tranzistorů na jednom čipu. Tento trend se pravděpodobně brzo zastaví z důvodů fyzikálních vlastností použitých technologií(velikost elektronu) Popisují předpověď růstu integrace tranzistorů na čipu. Tento zákon je platný skoro 50 let

4. Jakým způsobem se vyvíjely polovodičové technologie?

Velikost waferu, Výrobní proces, frekvence, Počet tranzistorů, Kapacita DRAM,Výkonová hustota

5. Napište čtyři hlavní skupiny obvodů ASIC (Aplikačně Specifické Integrované Obvody)

- Plně zákaznické obvody - Monolitické IO, většinou analogové obvody

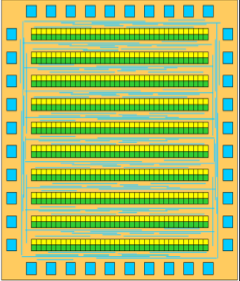

- Hradlová pole - Monolitické IO složené z řad nebo sloupců tranzistorů. Programují se pomocí masek propojení

- Standardní buňky - Monolitické IO navržené pomocí knihovních buňek

- Programovatelné obvody - Monolitické IO s tvořené logickými buňkami a bloky, které jsou zákaznicky programovány pomocí propojek

6. Co jsou plně zákaznické obvody, charakterizujte, jak se navrhují?

Jedná se o Monolitické IO, většinou analogové obvody

Je potřeba návrh celé topologie – všech vrstev

- Výborná flexibilita, limitováno pouze návrhovými pravidly

- Ruční návrh (některé digitální bloky mohou být automatizovány) – Návrhář nepoužívá předdefinované bloky z důvodu malé rychlosti, velké spotřeby atd.

- Analogový i digitální návrh dohromady

Vlastnosti:

- Dlouhý čas návrhu a technologické realizace

- Velice efektivní využití plochy čipu

- Levné pouze ve velikých sériích

Příklady:

- Analogové obvody, uP, paměti, převodníky, dekodéry….

7. Co jsou Hradlová pole, charakterizujte, jak se navrhují?

Prefabrikované čipy:

- Definované I/O obvody

- Jednotné pole tranzistorů propojovacích kanálů a propojek, tzv. primitivní buňky

- Funkční zapojení je realizováno pomocí jedné nebo více vrstev metalizace

Vlastnosti:

- Rychlá výroba

- Levné ve středních sériích

- Nevhodné pro realizaci RAM, PLA, ALU

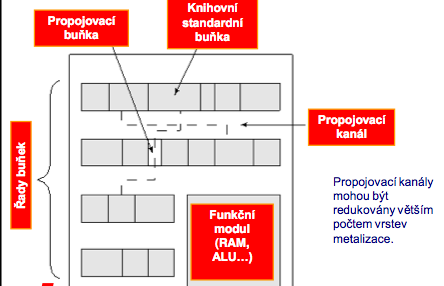

8. Co jsou Standardní buňky, charakterizujte, jak se navrhují?

Celý výrobní proces:

- Předdefinované knihovny základních buňek (NAND, NOR, OpAmp, Převodníky…)

- Návrhář definuje umístění a vzájemné propojení

- Mohou být digitální i analogové

Vlastnosti:

- Velikost čipu limituje funkčnost

- Dlouhý výrobní čas

- Levné ve velkých sériích

- Definována výška buňky – snadné skládání

- Lepší funkčnost při nižší ploše v porovnání s hradlovými poli (1:4)

9. Co jsou programovatelné obvody, charakterizujte, jak se navrhují?

Základem je univerzální logická struktura (matice AND propojená s maticí OR) Logická funkce je vytvořena promocí programovatelných propojek, jejichž přerušením se odpojí logické signály. Velice rychlý návrh a realizace

- PROM – Programmable Read Only Memory

- PAL – Programmable Array Logic

- PLA – Programmable Logic Array

- FPGA – Field programmable Gate Array

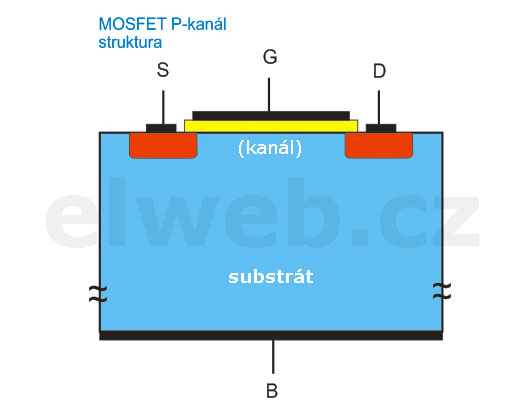

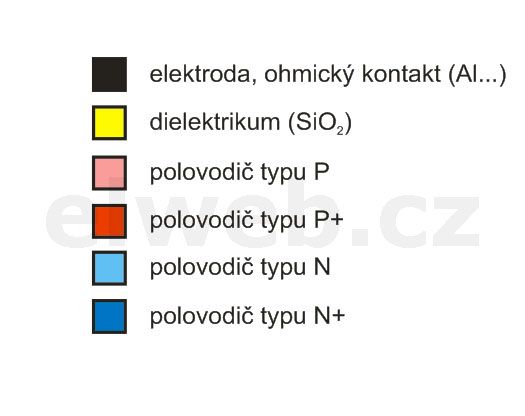

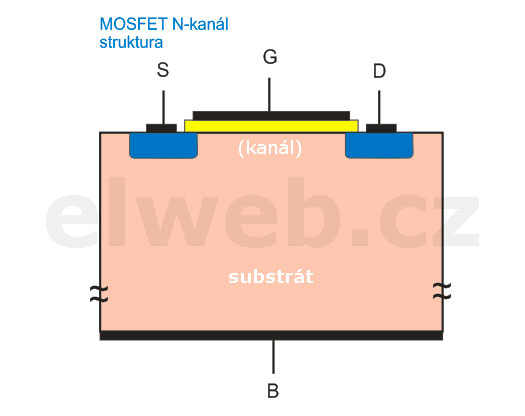

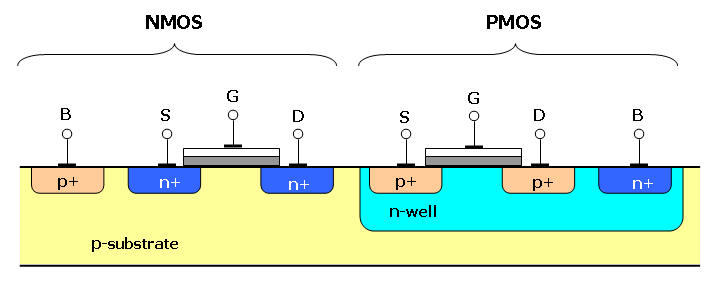

10. Nakreslete řez tranzistorem PMOS s jámou N i s kontaktem na jámu, nakreslete výstupní charakteristiky, vyznačte lineární a saturační oblast.

11. Nakreslete řez tranzistorem NMOS s jámou P i s kontaktem na jámu, nakreslete výstupní charakteristiky, vyznačte lineární a saturační oblast.

12. Co je prahové napětí, jak ho můžeme ovládat (technologicky).

Elektrické napětí, při kterém dojde ke zrušení/vytvoření hradlové vrstvy. Cca 1-3V. Napětí Ugs, při kterém se vytvoří kanál se nazývá prahové a značí se Ut (obvykle 1 až 3V)

13. Jaký je rozdíl mezi amorfním a monokrystalickým křemíkem? Jaké defekty v monokrystalu znáte?

- Amorfní – atomy Si-4 vazné, ale ne vždy se tak slučují, mají nepravidelnou strukturu (používá se k napařování tenkého filmu na fotovoltaické články )

- Monokrystal – křemík z taveniny, pravidelná struktura

Defekty v monokrystalu:

- Intersticiální poloha - atom je umístěn mimo mřížku (je navíc)

- Vakance - neobsazené mřížkové body – Atom chybí v mřížce

- Frenkelova porucha – Vakance + Intersticiální poloha

14. Co jsou tzv. čisté prostory, k čemu slouží?

Jedná se o výrobní prostory, při výrobě IO. Je tam mírný přetlak, vzduch filtrován, speciální obleky pro personál, počet prach částic 1-100.

15. Popište základní kroky přípravy křemíkových substrátů.

Růst monokrystalu – Ingot – odříznutí konců ingotu – výbrus fazet – nařezání destiček – broušení hran – broušení/lěštění – leptání - leštění – kontrola

16. Jak se vyrábějí křemíkové monokrystaly?

- Czochralského metoda

- Zonální tavba

17. Jaké druhy litografie znáte? Čím se liší?

- Fotolitografie do 0,1um

- Rentgenová litografie od 0,3um

- Elektronová litografie 10-100nm

liší se šířkou nejtenčí čáry na čipu

18. Jaký druh litografie používáme pro výrobu IO? Proč? Kde jsou její hranice použití?

Fotolitografie, momentálně nelevnější řešení, s relativně vysokou výtěžností (60 až 150 waferů za hodinu), vlnová délka 193nm stačí maximálně na výrobní proces 45nm, vylepšením na imerzní ( ponořené ) fotolitografii lze vytvářet čipy na technologii 32nm. Poté přijde EUV litografie (problé výtěžnost 10 waferů za hodinu)

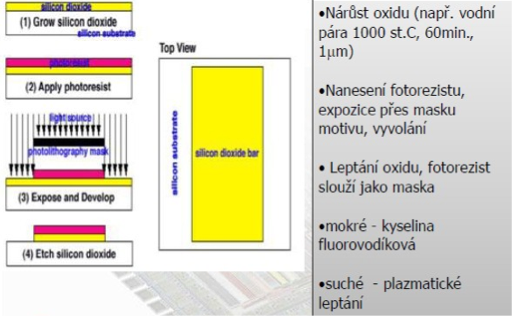

19. K čemu slouží fotolitografie v technologickém procesu IO?

K přenosu topologie čipu na křemíkový wafer

20. K čemu slouží leptání, jaké druhy znáte, co je selektivita a co anizotropie.

Odleptá SiO v oknech fotorezistu, ten se pak smyje v roztoku H2SO4 a H2O2

Druhy leptání:

- Mokré chemické leptání

- Plazmatické leptání

- reaktivní iontové leptání

Rozdíl:

- Selektivita – určuje jak efektivně je odstraňován leptaný materiál, bez toho aby leptal jiný materiál

- Anizotropie – rychlost leptání v různých směrech

21. Co je plazmatické leptání?

Suché leptání Leptání radikály fluoru, ionty jsou urychlovány napětím mezi plazmou a elektrodou, při dopadu odevzdají energii povrchovým atomům a erodují s nimi, leptání je vysokoselektivní a izotropni

22. Co je termická oxidace, jak se provádí?

- Proces při kterém se vytvoří na monokrystalu vrstva SiO2

- Provádí se v Oxidační (difuzní peci) teplota 400-1200°C, wafer se ofukuje horkým O2

23. K čemu slouží termická oxidace ve výrobním procesu IO?

K vytvoření izolační vrstvičky SiO2

24. Co je difúze, jak se provádí? 25. Co je rozdifundování příměsí?

Difúze: Je proces, při němž pronikají atomy dopantu pod povrch křemíkové desky ve vybraných oblastech Teplotou, časem a chemickým složením lze nastavit hloubku nadifundované vrstvy a koncentraci dopantu při povrchu, nebo-li „Prosakování“ atomů z vnějšku do struktury Si Z kapalného zdroje – N2 probublává skrz POCl3 a spolu s O2 se fouká na wafery

- Vakuová difuze – wafery v peci s miskou dopantu, za vysoké teploty se dopant odpaří a usadí na waferech

Rozdifundování příměsí: Mechanismus, kdy se atomy dopantu pohybují v křemíku i když právě nedifundují z okolí. Oxid na povrchu křemíkové desky musí být dostatečně tlustý (kolem 500 nm) aby přes něj atomy fosforu nepronikly. Prostě a jednoduše se fosfor po křemíku víc rozleze.

26. CO je iontová implantace, jak se provádí?

Atomy dopantu jsou nastříeny pod povrch křemíkové desky. Ionty dopantu jsou urychlené elektrickým polem a nasměrované k povrchu desky a proniknou do jisté hloubky pod povrch křemíku. Ionty jsou urychleny urychlovačem. Mezi elektrodami 50-200kV

27. CO je epitaxe, jak se provádí a k čemu hlavně slouží?

Epitaxe je narůstání vrstvy křemíku na povrchu křemíkové desky. Vrstva má stejné krystalografické vlastnosti jako podložka ale může mít jinou koncentraci příměsi anebo jiný příměsi. Používá se k vytvoření další vrstvy

28. Co je naprašování ve výrobním procesu IO?

Atomy kovu (Al. Cu, Au, Ti, …) jsou vyraženy rychlým atomem Ar (10ky km/s), ty se pak usadí na předmětech v okolí. Vzniká tak pokovení. Při klasickém naprašování je terč z vodivého materiálu umístěn ve vakuové komoře a je přiveden na vysoký záporný potenciál řádově tisíce voltů. Do komory se přes jehlový ventil připouští pracovní plyn (obvykle argon) a tlak se udržuje na hodnotě řádově jednotky pascalu. Před terčem se zapálí doutnavý výboj, přičemž kladné ionty bombardují záporný terč a záporné elektrony dopadají na uzemněnou kostru komory. Těžké ionty svým dopadem rozprašují terč a rozprášené atomy se usazují na vnitřních površích. Substráty se umísťují před terč, tenká vrstva tedy vzniká především na nich.

29. Co je chemické nanášení vrstev (CVD), k čemu se používá?

Chemical vapour deposition, do reakční zóny jsou přiváděny reakční složky v plynné fázi obvykle za sníženého tlaku a vrstva vzniká chemickou reakcí na zahřátém substrátu. Používá se k vytváření oxidačních příkopů, vytvoření k vytvoření metalizace, atd (prostě když je nějaká díra a potřebuje se zaplnit)

30. Co je chemicko-mechanická planarizace (CMP), proč se používá?

Leštění, Mechanicky s chemickým leptáním, nebo chemicky s mechanickým broušením

- planarizace povrchu s odstraněním přebytečného materiálu

- Chemická reakce naleptá a změkčí povrch deponovaného materiálu,potom se mechanickým broušením povrch planarizuje (zarovná)

Používá se k zarovnání povrchu.

31. Jaké vlastnosti musí mít ideální pouzdro pro integrovaný obvod?

- Elektrické – malé parazitní kapacity a indukčnosti

- Mechanické – pevnost a spolehlivost

- Tepelné – Dovbrý odvod tepla

- Ekonomické – levne

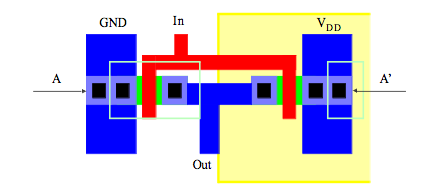

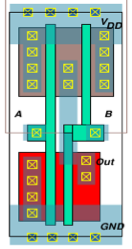

32. Nakreslete řez strukturou invertoru CMOS s N jámou i s kontakty na jámu a na substrát.

33. Nakreslete layout invertoru CMOS s N jámou i s kontakty na jámu a na substrát.

34. Jak se realizuje metalizace v integrovaných technologiích?

Depozice pomocí CVD, zalaštění pomocí CMP

35. Co jsou návrhová pravidla, proč je nutné je zavádět při návrhu IO?

Pravidla jak navrhovat strukturu, layout IO, při nedodržení může dojít k slití motivů, nebo nefunkčnosti zapojení, .

36. Jaké základní návrhová pravidla znáte?

- Min šířka motivu

- Min vzdál motivů

- Min a max rozměr motivu

- MInimální přesah

- Min separace dvou masek

- Návrhová pravidla λ

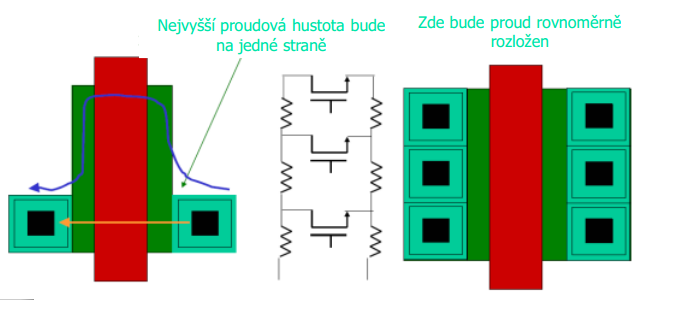

37. Nakreslete layout širokého tranzistoru rozděleného do dvou paralelních sekcí

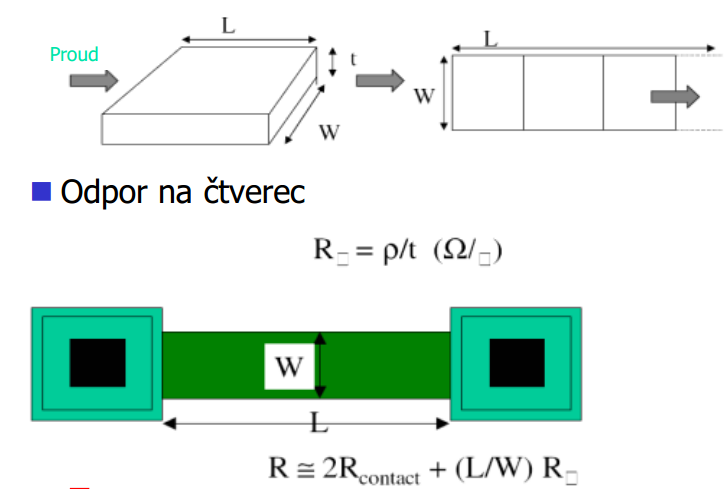

38. Nakreslete dva typy integrovaných rezistorů. Co je odpor na čtverec?

39. Jaké druhy integrovaných rezistorů znáte? Srovnejte jejich vlastnosti.

- Difuzni rezistory - realizovane pomoci difuznich oblasti(napetove zavisle)

- Poly rezistory - odpor, který se tvoří v polysiliconu

40. Nakreslete řez integrovaným rezistorem vytvořeným pomocí difúzní oblasti.

41. Jaké druhy integrovaných kapacitorů znáte? Srovnejte jejich vlastnosti.

42. Nakreslete řez dvěma typy integrovaných kapacitorů.

43. Co jsou návrhová pravidla? Co popisují? Jak se kontrolují?

popisují vzájemné sesazení masek kontaktu, poly Základní parametry jsou:

- minimální šířka motivu

- minimální vzdálenost motivu

- mimimální a maximální rozměr motivů

- minimální přesah motivu

- minimální separace 2 masek

Kontroluje se správá oritentace tranzistorů, vlivy teploty,

44. Co vše se změní (rozměry, dotace ...) u MOS tranzistoru zmenšíme-li jeho délku kanálu 2x?

Změna faktoru S. za S se dosazí násobek zmenšení.

- Délka kanálu L 1⁄2

- šířka kanálu W 1⁄2

- hradlový oxid tox 1⁄2

- Napájecí napětí Vdd 1⁄2

- Prahové napětí Vt 1⁄2

- Dotace substrátu Na 2

- ——————

- Proudový faktor beta 2

- Proud Ids 1/2

- Odpor 1

- Hradlová kapacita 1/2

- Zpoždění 1/2

- Hodinová frekvence 2

- Dynamické ztráty 1/2 (1/S^2)

- Plocha čipu 1/2 (1/S^2)

45. Jaké jsou pozitivní a jaké negativní důsledky zmenšování rozměrů tranzistorů?

- + Tranzistory rychlejší, klesá dynamická spotřeba, větší hustota tranzistorů na plochu

- – Roste proudová hustota a odpor kontaktu

46. Co je SOI technologie, jaké jsou klady jaké zápory?

SOI – křemík na izolantu (Silicon on Insulator)

- +Lepší výkon, díky eliminaci parazitních jevů(u CMOS o 25-30%)

- +Menší VDD (40-50%)

- +Lepší využití plochy – menší plocha izolac Redukovaný efekt zpětného hradla Zamezení svod proudu do substrátu Menší oblasti PN přechodů

- + Větší hustota integrace Zamezení Latch-up efektu Provozní teplota až 250°C Odolnost proti záření

- - Tepelné vlastnosti, Hystereze prahového napětí, Dražší substrát o 3-10% oproti CMOS

47. Co je technologie předepnutého křemíku (Strained Silicon), jaké má výhody?

Na Ge, se nechá epitaxně narůst Si (při 300-800°C), Využívá se rozdílné mřížkové konstanty (Si ma menší mřížku) – zvýší se pohyblivost elektronů a děr + 50%, náklady +2%, rychlost čipu +35%, jednoduchost, není třeba zmenšovat šířku oxidu, možnost s budou cí kombimcí s jinou technologií.

48. Jaký je postup návrhu digitálních obvodů?

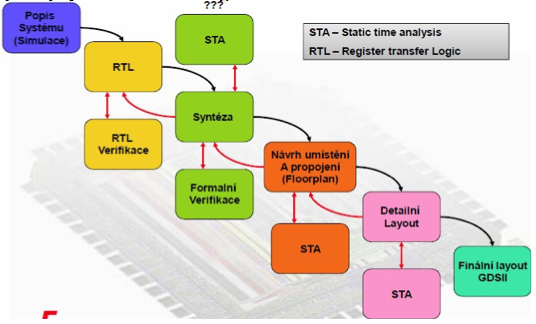

Logický návrh – Syntéza – Umístění propojení - Verifikace

49. Co je logický návrh, charakterizujte. Co jsou tzv. HDL jazyky?

Logický návrh – Vytvoření funčních specifikací verifikačního plánu, Systémové modelování, RTL popis a verifikace HDL, Verifikace na systémové úrovni, Pokročilé verifikační metody „Low power“

- HDL – číslicový, analogový a číslico-analogový jazyk pro chování elektronického obvodu

- * Rychlý popis fce obvodu, krátká doba symulace, hodí se i pro tvorbu simulačních obvodu

50. Co je syntéza v digitálním návrhu IO? Co je vstupem a co výstupem?

Načtení odladěného a verifikovaného HDL (VHDL nebo Verilog) kódu

Syntéza – Převedení zdrojového HDL kódu na netlist (zapojení systému)

Netlist je na úrovni logických hradel (NAND, NOR, XOR, registrů…)

Optimalizace návrhu – časování, plocha, spotřeba …

Fyzická syntéza – předběžné umístění bloků a hradel

Optimalizace kritických datových cest

51. Co je statická časová analýza (STA), k čemu slouží, kdy jí v návrhu provádíme?

Vhodná pro synchronní návrh, Kontroluje časování bez test vektorů, Konzervativní způsob v porovnávání s dynymickou čas. Analýzou

52. Načrtněte postup fyzického návrhu digitálního IO

53. Charakterizujte Plánování rozložení čipu (Floorplanning).

Cílem je umístit jednotlivé bloky a standardní buňky tak, aby propojovací nástroj rychle konvergoval. Jak se vypořádat s Velikostí čipu, Umístěním IO, Rozvodem hodinového signálu, Rozvodem VDD/GND

54. Načrtněte metody pro snížení spotřeby velkých digitálních IO.

- Multinapěťové bloky (každý blok je napájen jiným napětím podle potřeby)

- Multipaměťové bloky s vypínáním napájení - bloky které momentálně nepotřebuji mohu vypnout od napájení.

- * pozor na časovou prodlevu mezi zapnutím a použitím vypnutého bloku

55. Co jsou multi-napěťové bloky, proč je v návrhu digitálních IO uplatňujeme?

- uplatňují se kůli snížení spotřeby energie čipu

- viz otázka 54.

56. Co je makrobuňka? CO je tzv. IP blok?

- IP blok – blok, který se nechá zakoupit od třetích firem

- Makrobuňka – velký blok, možný problém s možnostmi propojeni

57. Čím se řídí a optimalizuje rozmístění buněk (Placement) v digitálním návrhu?

Časováním a následným propojením bloku

58. Co jsou knihovny standardních buněk? Jaké mají výhody?

- Knihovny st. b. - předem navržené layouty specifických log. Hradel

- Každá buňka má stejnou velikost, Dodáváno výrobcem IO

59. Co je tzv. Časová kritická cesta v digitálním návrhu? Jak se optimalizuje při fyzickém návrhu čipu?

- Čas. kritická cesta – cesta u které je důležitý co nejrychlejší průchod signálu

- Optimalizace – časování, hustota propojení, napájeni

60 Jak se postupuje při návrhu metalického propojení (Routing) v digitálním návrhu IO?

- Rozmístění a návrh hodin – Připojení Hodinových uzlů – Návrh globálního signálového propojení – Detailní signálové propojen-Design for manufacturing (DFM)

61. Jak vznikají přeslechy v IO? Jak bojujeme proti přeslechům v integrovaných obvodech?

Optimalizace – Vhodné vedení propojení, Zapojení driverů závisí na - Vzájemná kapacita, Celková kapacitapropojení, síla zdroje rušeni

62. Co charakterizuje „Návrh pro výrobní proces“ (DFM – Design for Manufacturing)?

Návrhové techniky pro technologické zpracování, mísí být vzaty už při návrhu

63. Proč je nutné provádět Analýzu úbytku napětí (IR Drop Analysis) v digitálním návrhu IO?

Protože je problém jak dostat do čipu 100A při 1V

64. Co je elektromigrace? Jak se projevuje a jak proti ní bojujeme?

Podstatou je pohyb nabité částice působením elektrického pole

65. Co je LVS (Layout vs Schema), jak to pracuje?

Srovnání layoutu a schematu, extrakce jednotlivých součástek a propojeních, tvorba netlistu, srovnání netlistu

66. Co je ERC (Elektrická kontrola) v digitálním návrhu?

Kontrola elektrických pravidel (ERC) – kontroluje zkraty a plovoucí uzly

67. Co jsou MEMS struktury, kde se používají?

- Mikro elektrické mechanické systémy – Motivy veliksti micrometru + Přesnost, nízké náklady, menší, lehčí mechanizmy,

- Aplikyce – madicína, atuomobily, průmysl,… - elektromechanické senzory Materiály – kovy, plasty, keramika, Si

- Struktua – Membrány, nosníky, trisky, pohony, vlnovody

68. Načrtněte postup výroby jednoduchého MEMS nosníku (PolySi nosník na křemíku).

69. Co je objemové leptání v MEMS technologiích?

Odleptání materiálu i pod součástkou (leptání koleček)

70. Jak fungují MEMS akcelerometry?

Fungují na kapacitním principu, 2 hřebeny v sobě – podle vychýlení plošek se určí akcelerace

71. Jak funguje MEMS gyroskop?

72. Jaké znáte optické MEMS

Mikromechanické zrcátko

73. Popište postup návrhu a simulací MEMS struktur

- Příprava – příprava geometrického modelu, určí se materiálové konstaty, tvorba diskretizační sítě, zadání parametrů simulace

- Zpracování – vlastní výpočet, definují se okrajové podmíky a parametry simulace

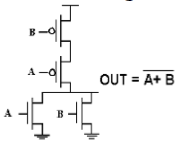

74. Nakreslete schéma zapojení dvoustopého hradla NAND v CMOS technologii.

75. Nakreslete schéma zapojení dvoustopého hradla NOR v CMOS technologii.

76. Nakreslete layout dvoustopého hradla NAND v CMOS technologii.

77. Nakreslete layout dvoustopého hradla NOR v CMOS technologii.

78. Jak se postupuje při výrobě masek pro optickou litografii?

Masky pro optickou litografii mívají 8 vrstev, které se tvoří postupně:

- Aktivní oblasti

- P-jáma implantace

- N-jáma implantace

- Poly gate

- N+ S/D implantace

- P+ S/D implantace

- Kontaktní okna

- Metalizace